Product Descriptions

RK2818 is a highly-integrated, high-performance, low-power digital multimedia processor which is based on Dual Core (DSP+CPU) architecture with hardware accelerator. It is designed for high-end multimedia product applications such as MID, AP, GPS and Mobile TV etc.

RK2818 can support decode for various types of video standards such as H.264 /RMVB/MPEG-4/AVS/VC1/MPEG-2 by software and dedicated coprocessors, and encode for some video standards by software. Specially, highest performace for video decode will reach fluent replay for video with H.264 @ 1280x720 formats. RK2818 also provides strong graphics/image ability with embedded GPU. By providing a complete set of peripheral interface, RK2818 can support very flexible applications, including SDRAM/ Mobile SDRAM/DDRII/Mobile DDR, Nor Flash, Nand Flash, LCDC, Sensor, USB OTG 2.0/USB Host 1.0, SD/MMC/SDIO, Wi-Fi, High-speed ADC, I2C, I2S, UART, SPI, PWM etc.

Product Features

System Operation

Dual Core Architecture (ARM9 + DSP) , including hardware accelerator

Support system boot sequentially from ARM to DSP

Support address remap function

For two cores, all modules have unified address space

Selectable JTAG debug method

ARM9 debug only (default)

DSP debug only

ARM9+DSP dual core debug

Selectable CPU booting method

Boot from NOR Flash

Boot from Nand Flash

Boot from SPI nor flash

Boot from UART device

Boot from Host interface

Memory Organization

Internal memory space for ARM processor

Internal 16KB SRAM for ARM9 ICache

Internal 16KB SRAM for ARM9 DCache

Internal 8KB SRAM for ARM9 ITCM

Internal 16KB SRAM for ARM9 DTCM

Internal memory space for DSP processor

Internal 96KB SRAM for DSP Instruction L1 Memory (Also config as 32KB Memory+32KB ICache by software, another 32KB is switched by software)

Internal 64KB SRAM for DSP Data L1 Memory

Internal 48KB SRAM for DSP Instruction L2 Memory

Internal 32KB SRAM for DSP Data L2 Memory

Embedded 8KB ROM for CPU Boot

Embedded 4KB SRAM for communication between two cores

Embedded 48KB SRAM for share among CPU,DSP and LCDC rotator

Processors

ARM926EJC

RISC architecture with 32bit ARM and 16bit Thumb instruction sets

Include efficient execution of Java byte codes

Built-in MMU to provide flexible memory management needed by many mainstream OS

Harvard cached architecture , separate ICache and DCache

Separate instruction and data TCM interfaces

Separate instruction and data AHB bus interface

Support ARM debug architecture

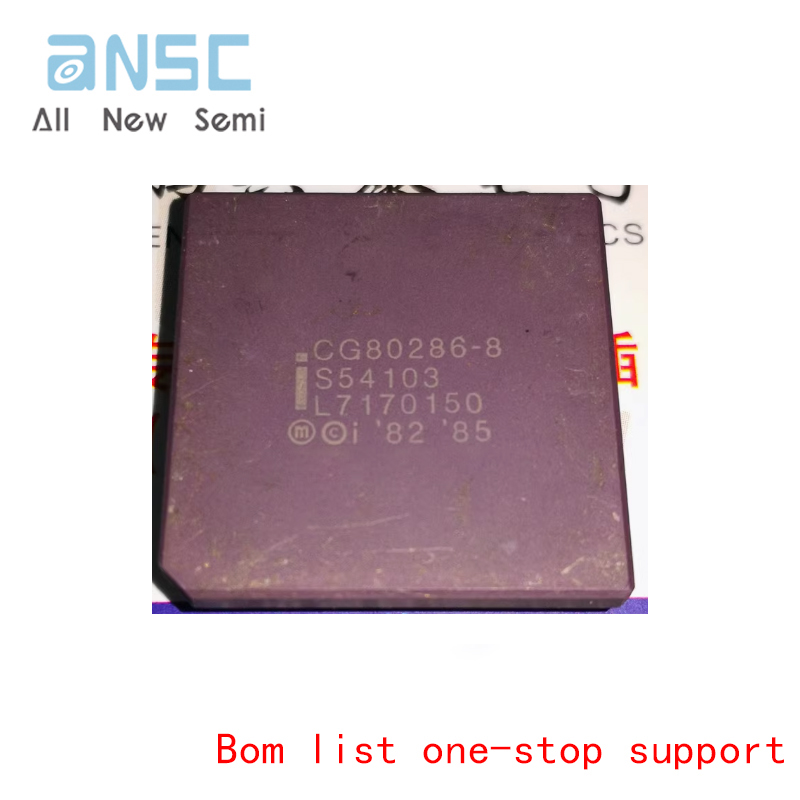

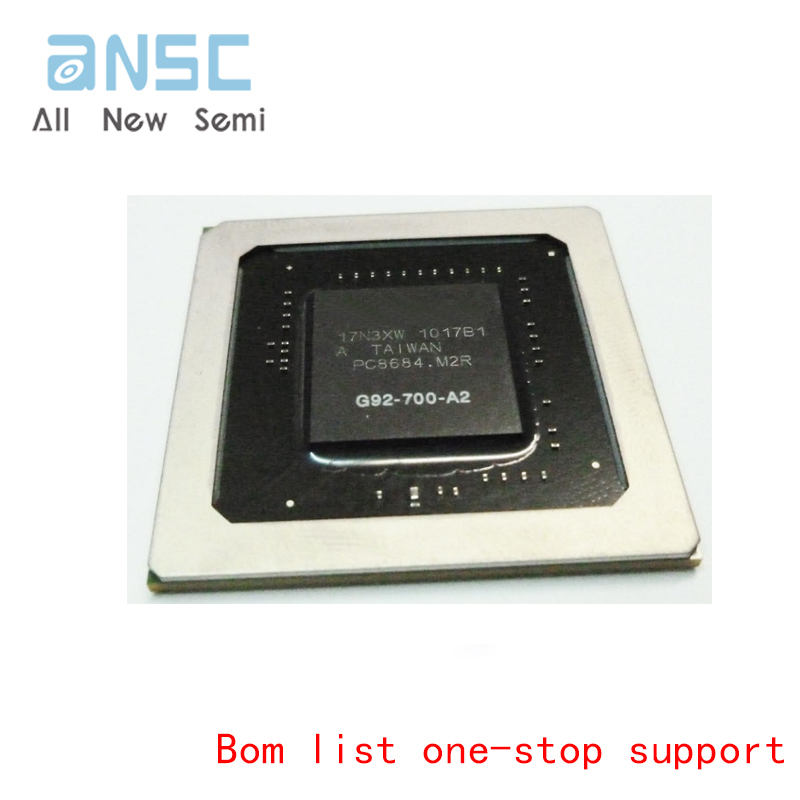

Actual product photos

Product Data Manual:

For more product information, please download the PDF

Payment&Transportation

Official Certificate&Certificate

Multiple product supply

Company office environment

Warehouse Real Shot

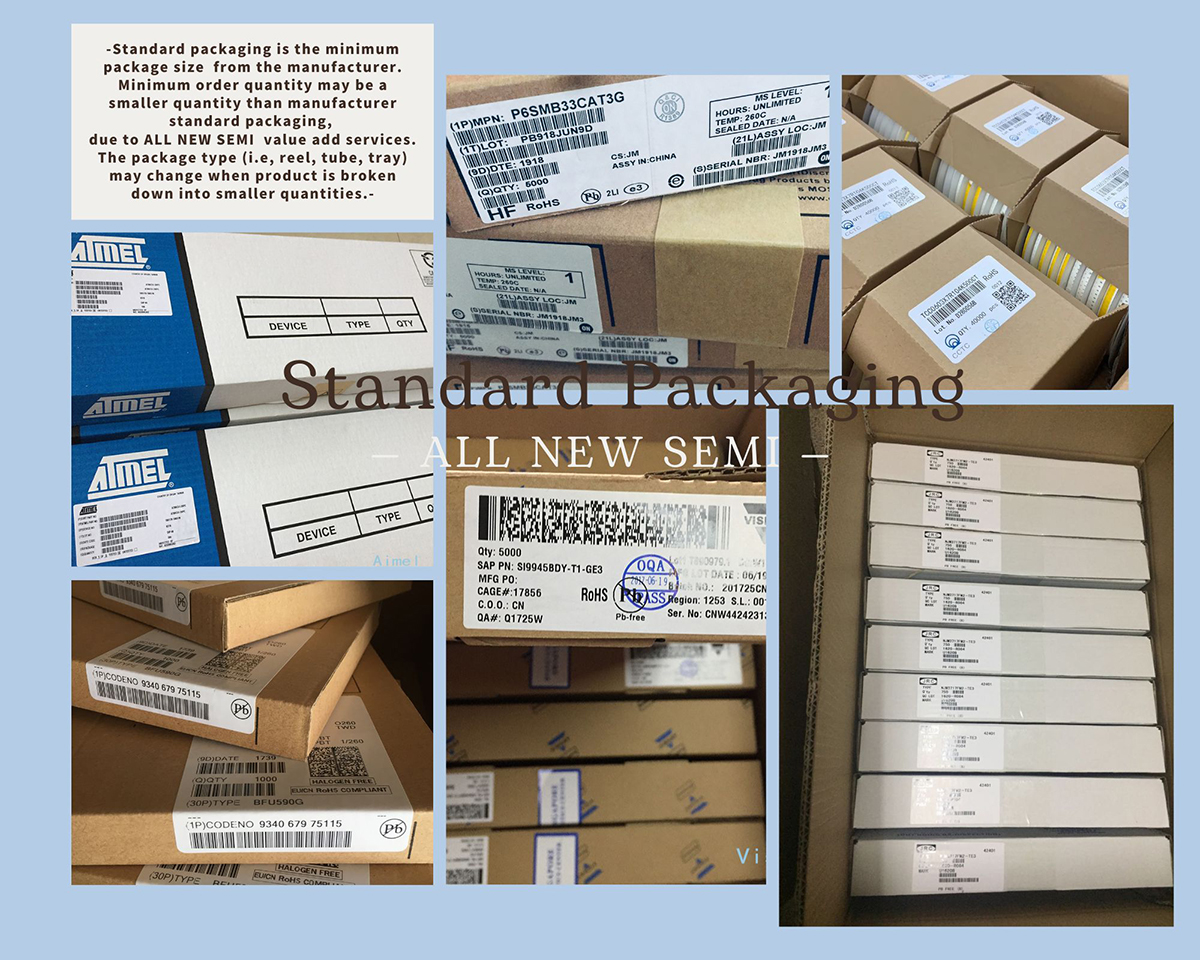

Standard packaging

We also provide :

| Part No | Manufacturer | Date Code | Quantity | Description |

| LM22676ADJ | NS | 19+ | 250 | SOP8 |

| TPS562201DDCR | TI | 22+ | 795500 | SOT23-6 |

| NJG1806K75 | JRC | 22+ | 500000 | DFN6 |

| TLV74318PDQNR | TI | 22+ | 402000 | X2SON-4 |

| NJG1801K75 | JRC | 22+ | 300000 | SMD |

| NJG1804K64 | JRC | 22+ | 300000 | DFN8 |

| LM27761DSGR | TI | 22+ | 151000 | WSON8 |

| TLV62565DBVR | TI | 22+ | 138000 | SOT23-5 |

| TPS613222ADBVR | TI | 22+ | 108000 | SOT23-5 |

| LNK625DG-TL | POWER | 22+ | 100000 | SOP-8 |

| OPA4322AIPWR | TI | 22+ | 100000 | TSSOP14 |

| TLV75528PDRVR | TI | 22+ | 99000 | WSON-6 |

| TPS7A2025PDQNR | TI | 22+ | 78500 | X2SON-4 |

| TLV62568DBVR | TI | 22+ | 72000 | SOT23-5 |

| STM32L051K8U6TR | ST | 22+ | 60000 | QFN32 |

| SKY66421-11 | SKYWORKS | 22+ | 56500 | QFN16 |

| TPS7A1111PDRVR | TI | 22+ | 54000 | WSON6 |

| TLV62569PDDCR | TI | 22+ | 52000 | SOT23-6 |

| TLV62569DBVR | TI | 22+ | 48000 | SOT23-5 |

| TPS23753APWR | TI | 22+ | 40000 | TSSOP14 |

| NB691GG-Z | MPS | 22+ | 30000 | QFN |

| SN74AHC1G02DBVR | TI | 22+ | 27939 | SOT-23 |

| TPS63000DRCR | TI | 22+ | 23238 | VSON10 |

| TLV75533PDRVR | TI | 22+ | 21500 | WSON6 |

| NB687BGQ-Z | MPS | 22+ | 20000 | QFN |

| A3916GESTR-T-1 | ALLEGRO | 22+ | 17150 | QFN-20 |

| TPS62135RGXR | TI | 22+ | 15000 | VQFN11 |

| TLE2022AMDR | TI | 0803+ | 12500 | SOP8 |

| TPS23756PWPR | TI | 22+ | 12000 | HTSSOP-20 |