KS8995MAI Product details

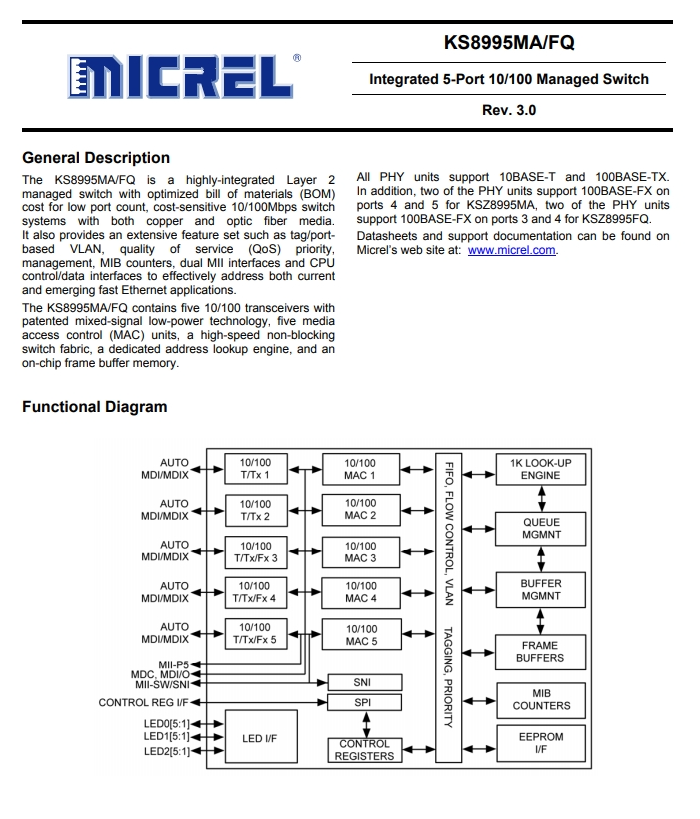

General Description

The KS8995MA/FQ is a highly-integrated Layer 2 managed switch with optimized bill of materials

(BOM) cost for low port count, cost-sensitive 10/100Mbps switch systems with both copper and

optic fiber media. It also provides an extensive feature set such as tag/port based VLAN,

quality of service (QoS) priority, management, MIB counters, dual MII interfaces and CPU

control/data interfaces to effectively address both current and emerging fast Ethernet applications.

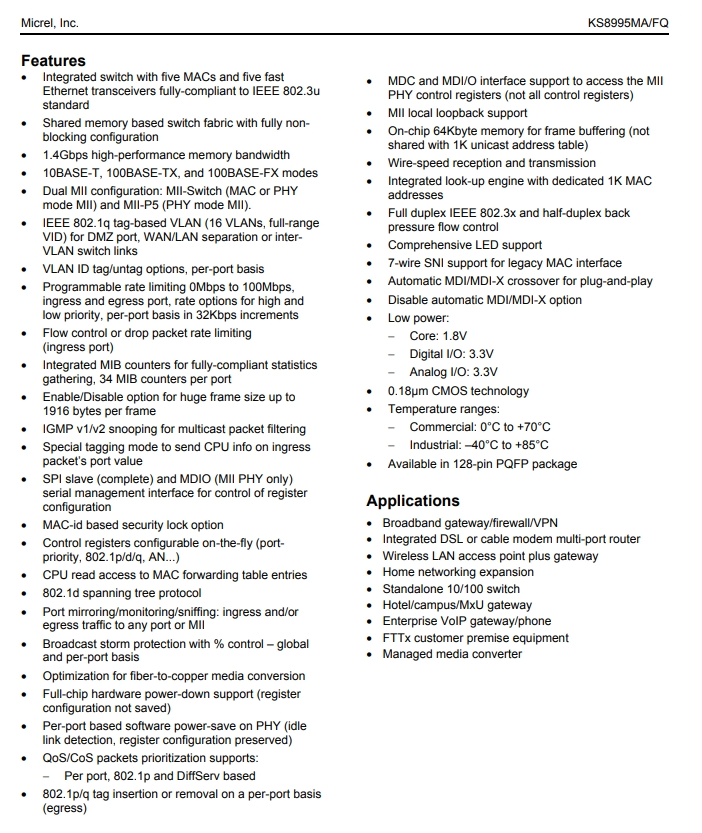

Features

• Integrated switch with five MACs and five fast Ethernet transceivers fully-compliant to IEEE 802.3u standard

• Shared memory based switch fabric with fully non blocking configuration

• 1.4Gbps high-performance memory bandwidth

• 10BASE-T, 100BASE-TX, and 100BASE-FX modes

• Dual MII configuration: MII-Switch (MAC or PHY mode MII) and MII-P5 (PHY mode MII).

• IEEE 802.1q tag-based VLAN (16 VLANs, full-range VID) for DMZ port,

WAN/LAN separation or inter VLAN switch links

• VLAN ID tag/untag options, per-port basis

• Programmable rate limiting 0Mbps to 100Mbps, ingress and egress port,

rate options for high and low priority, per-port basis in 32Kbps increments

• Flow control or drop packet rate limiting (ingress port)

• Integrated MIB counters for fully-compliant statistics gathering, 34 MIB counters per port

• Enable/Disable option for huge frame size up to 1916 bytes per frame

• IGMP v1/v2 snooping for multicast packet filtering

• Special tagging mode to send CPU info on ingress packet’s port value

• SPI slave (complete) and MDIO (MII PHY only) serial management interface for

control of register configuration

• MAC-id based security lock option

• Control registers configurable on-the-fly (port priority, 802.1p/d/q, AN...)

• CPU read access to MAC forwarding table entries

• 802.1d spanning tree protocol

• Port mirroring/monitoring/sniffing: ingress and/or egress traffic to any port or MII

• Broadcast storm protection with % control – global and per-port basis

• Optimization for fiber-to-copper media conversion

• Full-chip hardware power-down support (register configuration not saved)

• Per-port based software power-save on PHY (idle link detection, register configuration preserved)

• QoS/CoS packets prioritization supports:

− Per port, 802.1p and DiffServ based

• 802.1p/q tag insertion or removal on a per-port basis (egress)

• MDC and MDI/O interface support to access the MII PHY control registers (not all control registers)

• MII local loopback support

• On-chip 64Kbyte memory for frame buffering (not shared with 1K unicast address table)

• Wire-speed reception and transmission

• Integrated look-up engine with dedicated 1K MAC addresses

• Full duplex IEEE 802.3x and half-duplex back pressure flow control

• Comprehensive LED support

• 7-wire SNI support for legacy MAC interface

• Automatic MDI/MDI-X crossover for plug-and-play

• Disable automatic MDI/MDI-X option

• Low power:

− Core: 1.8V

− Digital I/O: 3.3V

− Analog I/O: 3.3V

• 0.18µm CMOS technology

• Temperature ranges:

− Commercial: 0°C to +70°C

− Industrial: –40°C to +85°C

• Available in 128-pin PQFP package

Applications

• Broadband gateway/firewall/VPN

• Integrated DSL or cable modem multi-port router

• Wireless LAN access point plus gateway

• Home networking expansion

• Standalone 10/100 switch

• Hotel/campus/MxU gateway

• Enterprise VoIP gateway/phone

• FTTx customer premise equipment

• Managed media converter

Product Description

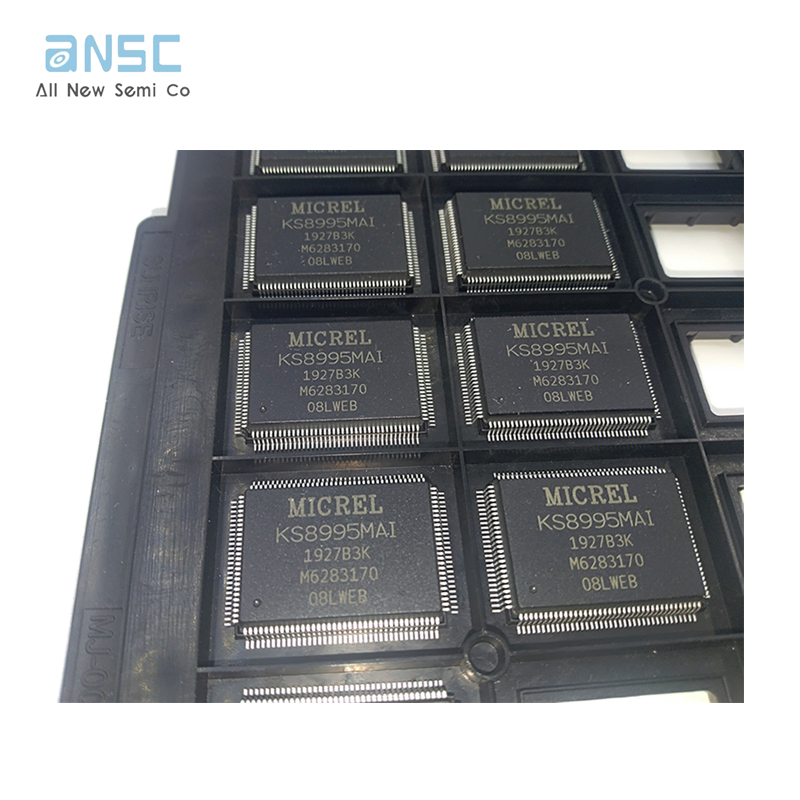

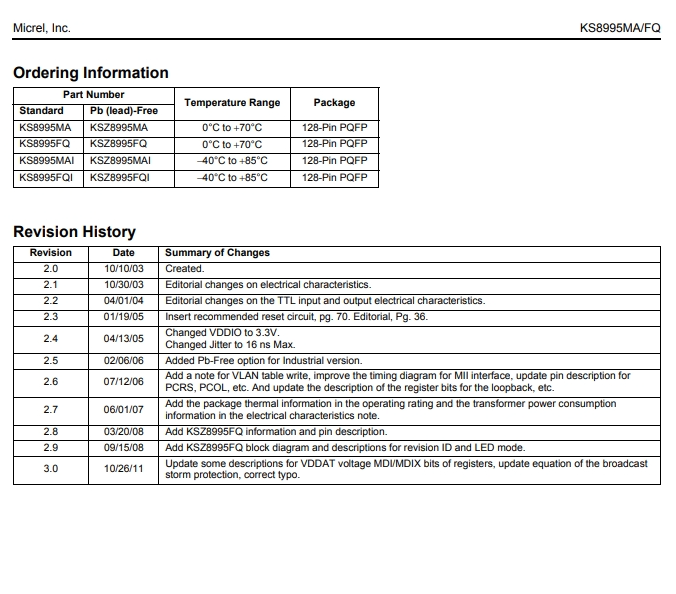

ANSC PART# | ANSC- KS8995MAI |

Part# | KS8995MAI |

Type: | Integrated Circuits |

Manufactor | MICRON |

DC | new |

Actual image of the product

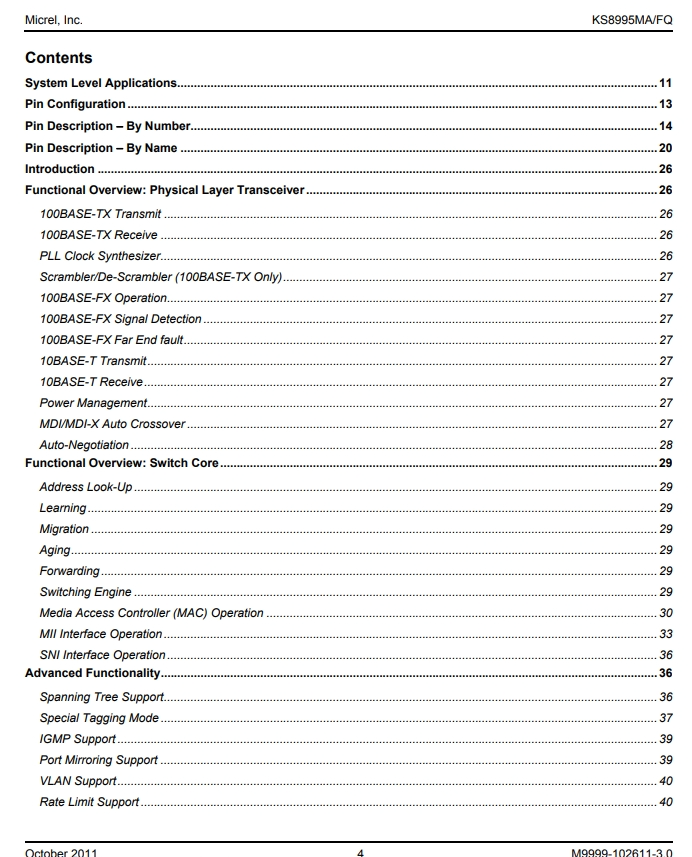

Product datasheet

For more information, please download

Payment&Transportation

Official Certificate&Certificate

Standard packaging

Multiple product supply

Welcome to visit our company

Warehouse Real Shot