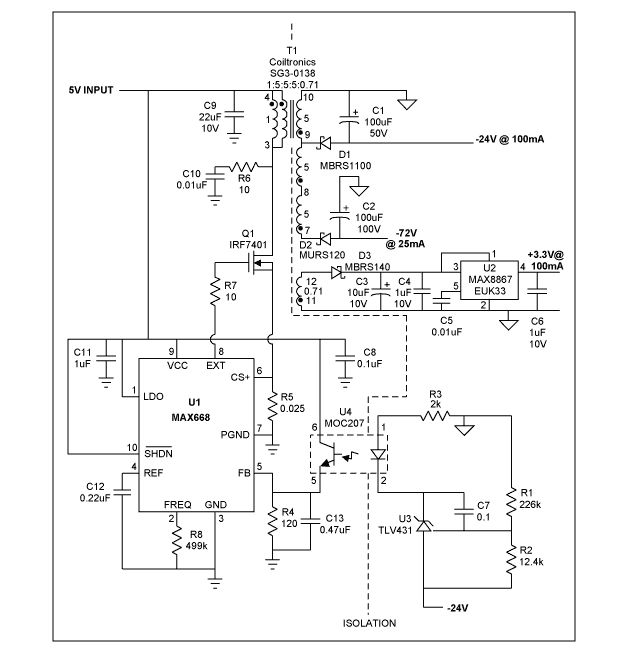

This application note shows a power supply that generates three isolation voltages for a slice. The isolation power supply uses a boost controller MAX668 with a flyback transformer for -24V and -72V outputs, and uses an optocoupler to isolate the feedback signal. The linear regulator MAX8867 provides a 3.3V output.

Some user line interface cards (SLICs) require power supply voltage to be isolated from local power sources. The circuit in Figure 1 generates three isolation voltages from a 5V input:+3.3V at 100mA, -24V at 100mA, and -72V at 25mA. It has a boost controller (U1) that operates in a transformer flyback topology and an optocoupler for isolating feedback signals. To provide this feedback (from -24V output to boost controller), the optocoupler (U4) is driven by a shunt regulator (U3) as an error amplifier.

The SLIC power supply shown in Figure 1 uses a transformer to isolate three outputs (+3.3V, -24V, and -72V), and uses an optocoupler to isolate the feedback signal.

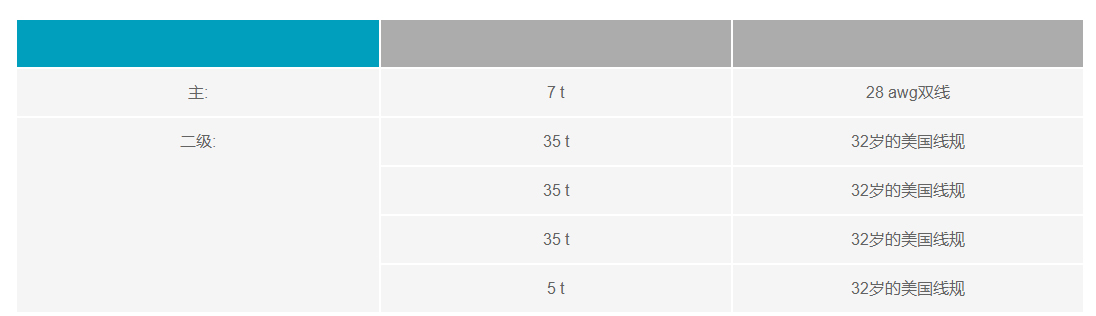

A custom transformer is required for a wide range of output voltage. Its core is a standard geometric coil SG3-0138 with a (L)=138nH/T ²。 The primary inductance is 6.8 µ H, and the peak current is 4A. The primary to secondary turn ratio is 1:5, so in order to achieve optimal efficiency, the duty cycle of the converter is close to 50%. The non regulated -72V output is derived from the regulated -24V output through three identical secondary windings connected in series. There is also a tap for -48V output, as well as a low-voltage winding that drives a linear regulator (U2) to provide+3.3V output. The winding specifications of the transformer are:

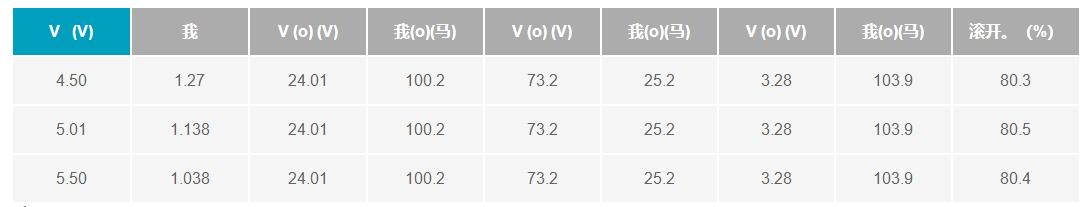

At the maximum specified load, the circuit outputs 5.0V at 1.138A,+3.28V at 103.9mA, -24.0V at 100mA, and -73.2V at 25.2mA, with an efficiency of 80%.

Note:

T1 wrapped around 138nH/T ² On the standard geometric core.

The primary inductance is 6.7 µ H.

Mainly on the 7th wheel and the 28th double track.

The secondary layer is three layers, with 35 times per layer and 32 times each time.

Low voltage secondary is 5 turns 32 #.

Declaration: The views expressed in this article only represent the author and do not represent the views and positions of ANSC. If there are any infringement or other issues, please contact our website for modification or deletion.