Product Descriptions

Multi-purpose, Feature Rich ExpressLane™ PCI Express Switch

The ExpressLane PEX 8518 device offers PCI Express switching capability enabling users to add scalable high bandwidth, non-blocking interconnection to a wide variety of applications including servers, storage systems, communications platforms, blade servers, and embedded-control products. The PEX 8518 is well suited for fan-out, aggregation, peer-to peer, and intelligent I/O module applications.

Highly Flexible Port Configurations

The PEX 8518 offers highly configurable ports. There are a maximum of five ports that can be configured to any legal width from x1 to x8, in any combination to support your specific bandwidth needs. The ports can be configured for symmetric (each port having the same lane width and traffic load) or asymmetric (ports having different lane widths) traffic. In the event of asymmetric traffic, the PEX 8518 features a flexible central packet memory that allocates a memory buffer for each port as required by the application or endpoint. This buffer allocation along with the device's flexible packet flow control minimizes bottlenecks when the upstream and aggregated downstream bandwidths do not match (are asymmetric). Any of the ports can be designated as the upstream port, which can be changed dynamically.

End-to-end Packet Integrity

The PEX 8518 provides end-to-end CRC protection (ECRC) and Poison bit support to enable designs that require guaranteed error-free packets. These features are optional in the PCI Express specification, but PLX provides them across its entire ExpressLane switch product line.

Non-Transparent “Bridging” in a PCI Express Switch

The PEX 8518 supports full non-transparent bridging (NTB) functionality to allow implementation of multi-host systems and intelligent I/O modules in applications such as communications, storage, and blade servers. To ensure quick product migration, the non-transparency features are implemented in the same fashion as in standard PCI applications. Non-transparent bridges allow systems to isolate memory domains by presenting the processor subsystem as an endpoint, rather than another memory system. Base address registers are used to translate addresses; doorbell registers are used to send interrupts between the address domains; and scratchpad registers are accessible from both address domains to allow inter-processor communication.

Two Virtual Channels

The ExpressLane PEX 8518 switch supports two full-featured Virtual Channels (VCs) and eight Traffic Classes (TCs). The mapping of Traffic Classes to port-specific Virtual Channels allows for different mappings for different ports. In addition, the devices offer user-selectable Virtual Channel arbitration algorithms to enable users to fine tune the Quality of Service (QoS) required for a specific application.

Product Features

PEX 8518 General Features

o 16-lane PCI Express switch - Integrated SerDes

o Up to five configurable ports

o 23mm x 23mm, 376-ball PBGA package

o Typical Power: 2.6 Watts

PEX 8518 Key Features

o Standards Compliant

- PCI Express Base Specification, r1.1

- Standard SHPC Specification, r1.1 (hot-plug)

o High Performance

- Non-blocking internal architecture

- Full line rate on all ports

- Cut-Thru latency: 150ns

o Non-Transparent Bridging

- Configurable Non-Transparent port for Multi-Host or Intelligent I/O Support

o Flexible Configuration

- Five highly flexible & configurable ports (x1, x2, x4, or x8)

- Configurable with strapping pins, EEPROM, I2 C, or Host software

- Lane and polarity reversal

o PCI Express Power Management

- Link power management states: L0, L0s, L1, L2/L3 Ready, L2 and L3

- Device states: D0 and D3hot

- Vaux, WAKE#, Beacon support

o Spread Spectrum Clock

- Dual clock domain

o Quality of Service (QoS)

- Two Virtual Channels per port

- Eight Traffic Classes per port

- Fixed and Round-Robin Virtual Channel Port Arbitration

o Reliability, Availability, Serviceability

- 5 Standard Hot-Plug Controllers

- Upstream port as hot-plug client

- Transaction Layer end-to-end CRC

- Poison bit

- Advanced Error Reporting

- Lane Status bits and GPO available

- Per port error diagnostics

• Bad DLLPs

• Bad TLPs

• CRC errors

- JTAG boundary scan

- Fatal Error out-of-band signal option

Product Applications

Suitable for host-centric as well as intelligent I/O

applications ExpressLane PEX 8518 can be configured for a wide variety of form factors and applications.

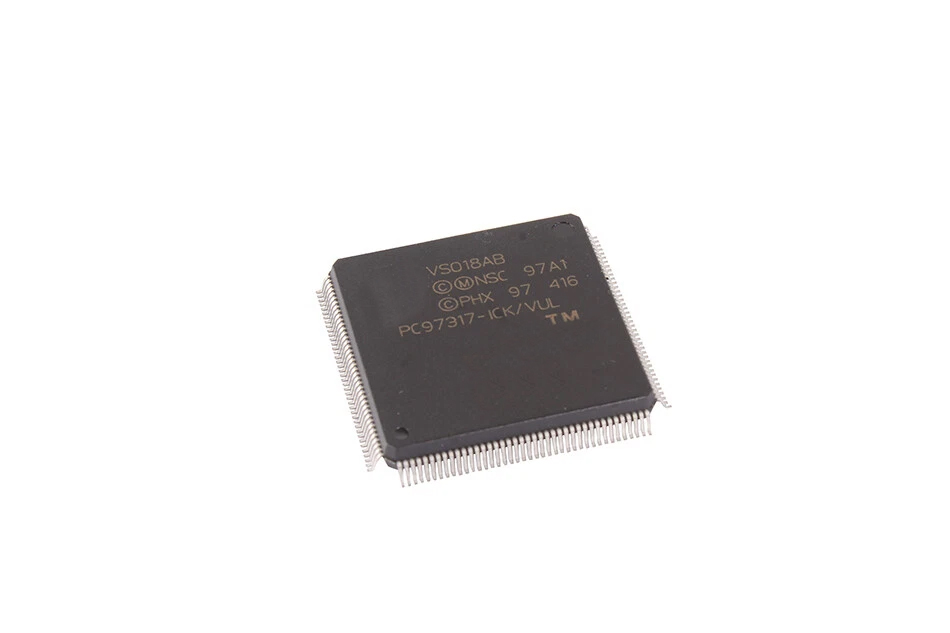

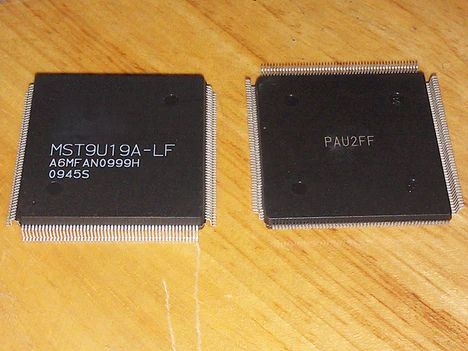

Actual product photos

Payment&Transportation

Official Certificate&Certificate

Multiple product supply

Company office environment

Warehouse Real Shot

Standard packaging

We also provide :

| Part No | Manufacturer | Date Code | Quantity | Description |

| LM22676ADJ | NS | 19+ | 250 | SOP8 |

| TPS562201DDCR | TI | 22+ | 795500 | SOT23-6 |

| NJG1806K75 | JRC | 22+ | 500000 | DFN6 |

| TLV74318PDQNR | TI | 22+ | 402000 | X2SON-4 |

| NJG1801K75 | JRC | 22+ | 300000 | SMD |

| NJG1804K64 | JRC | 22+ | 300000 | DFN8 |

| LM27761DSGR | TI | 22+ | 151000 | WSON8 |

| TLV62565DBVR | TI | 22+ | 138000 | SOT23-5 |

| TPS613222ADBVR | TI | 22+ | 108000 | SOT23-5 |

| LNK625DG-TL | POWER | 22+ | 100000 | SOP-8 |

| OPA4322AIPWR | TI | 22+ | 100000 | TSSOP14 |

| TLV75528PDRVR | TI | 22+ | 99000 | WSON-6 |

| TPS7A2025PDQNR | TI | 22+ | 78500 | X2SON-4 |

| TLV62568DBVR | TI | 22+ | 72000 | SOT23-5 |

| STM32L051K8U6TR | ST | 22+ | 60000 | QFN32 |

| SKY66421-11 | SKYWORKS | 22+ | 56500 | QFN16 |

| TPS7A1111PDRVR | TI | 22+ | 54000 | WSON6 |

| TLV62569PDDCR | TI | 22+ | 52000 | SOT23-6 |

| TLV62569DBVR | TI | 22+ | 48000 | SOT23-5 |

| TPS23753APWR | TI | 22+ | 40000 | TSSOP14 |

| NB691GG-Z | MPS | 22+ | 30000 | QFN |

| SN74AHC1G02DBVR | TI | 22+ | 27939 | SOT-23 |

| TPS63000DRCR | TI | 22+ | 23238 | VSON10 |

| TLV75533PDRVR | TI | 22+ | 21500 | WSON6 |

| NB687BGQ-Z | MPS | 22+ | 20000 | QFN |

| A3916GESTR-T-1 | ALLEGRO | 22+ | 17150 | QFN-20 |

| TPS62135RGXR | TI | 22+ | 15000 | VQFN11 |

| TLE2022AMDR | TI | 0803+ | 12500 | SOP8 |

| TPS23756PWPR | TI | 22+ | 12000 | HTSSOP-20 |