Product Features

Single-chip Peripheral Component Interconnect (PCI) Bus multi-channel HDLC controller.

Supports up to 128 bi-directional HDLC channels assigned to a maximum of 8 channelised T1 or E1 links. The number of time-slots assigned to an HDLC channel is programmable from 1 to 24 (for T1) and from 1 to 31 (for E1).

Supports up to 8 bi-directional HDLC channels each assigned to an unchannelised arbitrary rate link; subject to a maximum aggregate link clock rate of 64 MHz in each direction. Channels assigned to links 0 to 2 can have a clock rate of up 52 MHz when SYSCLK is at 33 MHz. Channels assigned to links 3 to 7 can have a clock rate of up to 10 MHz.

Supports up to two bi-directional HDLC Channels each assigned to an unchannelised arbitrary rate link of up to 52 MHz when SYSCLK is at 33 MHz.

Supports a mix of up to 8 channelised and unchannelised links; subject to the constraint of a maximum of 128 channels and a maximum aggregate link clock rate of 64 MHz in each direction.

For each channel, the HDLC receiver performs flag sequence detection, bit de-stuffing, and frame check sequence validation. The receiver supports the validation of both CRC-CCITT and CRC-32 frame check sequences. The receiver also checks for packet abort sequences, octet aligned packet length and for minimum and maximum packet length.

Alternatively, for each channel, the receiver supports a transparent mode where each octet is transferred transparently to host memory. For channelised links, the octets are aligned with the receive time-slots.

For each channel, time-slots are selectable to be in 56 kbits/s format or 64 kbits/s clear channel format.

For each channel, the HDLC transmitter performs flag sequence generation, bit stuffing, and, optionally, frame check sequence generation. The transmitter supports the generation of both CRC-CCITT and CRC-32 frame check sequences. The transmitter also aborts packets under the direction of the host or automatically when the channel underflows.

Supports two levels of non-preemptive packet priority on each transmit channel. Low priority packets will not begin transmission until all high priority packets are transmitted.

Alternatively, for each channel, the transmitter supports a transparent mode where each octet is inserted transparently from host memory. For channelised links, the octets are aligned with the transmit time-slots.

Directly supports a 32-bit, 33 MHz PCI 2.1 interface for configuration, monitoring and transfer of packet data, with an on-chip DMA controller with scatter/gather capabilities.

Provides 8 kbytes of on-chip memory for partial packet buffering in each direction. This memory can be configured to support a variety of different channel configurations from a single channel with 8 kbytes of buffering to 128 channels, each with a minimum of 48 bytes of buffering.

Supports PCI burst sizes of up to 128 bytes for transfers of packet data.

Pin compatible with PM7364 (FREEDM-32) device.

Provides a standard 5 signal P1149.1 JTAG test port for boundary scan board test purposes.

Supports 3.3 and 5 Volt PCI signaling environments.

Low power CMOS technology.

256 pin enhanced ball grid array (SBGA) or 272 pin plastic ball grid array (PBGA) packages (27 mm X 27 mm).

Product Applications

IETF PPP interfaces for routers

Frame Relay interfaces for ATM or Frame Relay switches and multiplexors

FUNI or Frame Relay service inter-working interfaces for ATM switches and multiplexors.

D-channel processing in ISDN terminals and switches.

Internet/Intranet access equipment.

Packet-based DSLAM equipment.

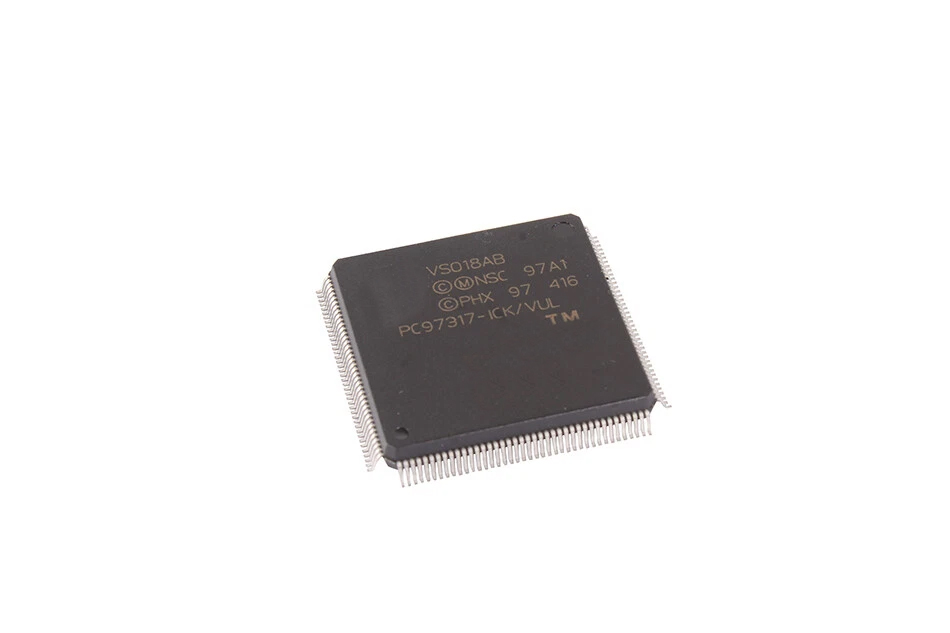

Actual product photos

Payment&Transportation

Official Certificate&Certificate

Multiple product supply

Company office environment

Warehouse Real Shot

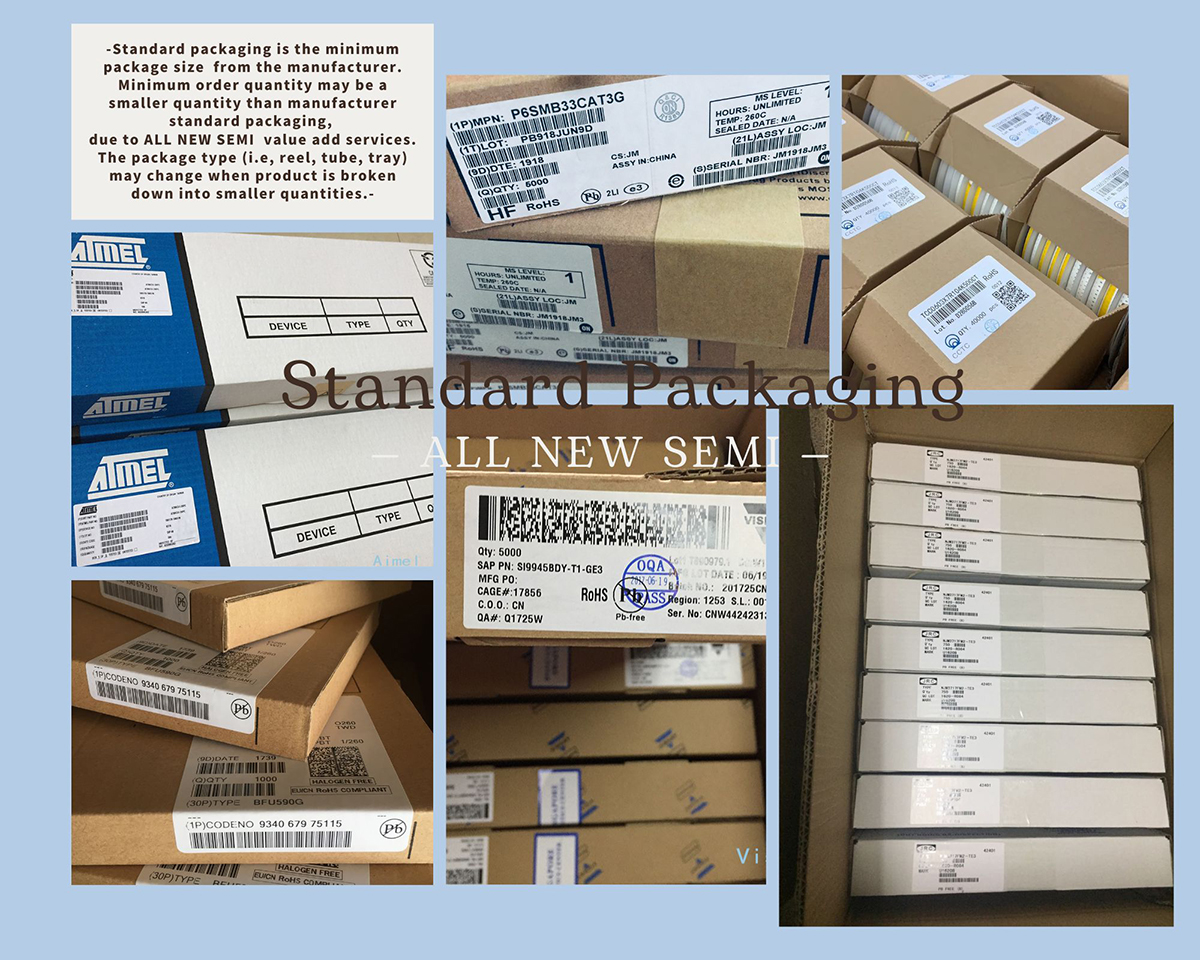

Standard packaging

We also provide :

| Part No | Manufacturer | Date Code | Quantity | Description |

| LM22676ADJ | NS | 19+ | 250 | SOP8 |

| TPS562201DDCR | TI | 22+ | 795500 | SOT23-6 |

| NJG1806K75 | JRC | 22+ | 500000 | DFN6 |

| TLV74318PDQNR | TI | 22+ | 402000 | X2SON-4 |

| NJG1801K75 | JRC | 22+ | 300000 | SMD |

| NJG1804K64 | JRC | 22+ | 300000 | DFN8 |

| LM27761DSGR | TI | 22+ | 151000 | WSON8 |

| TLV62565DBVR | TI | 22+ | 138000 | SOT23-5 |

| TPS613222ADBVR | TI | 22+ | 108000 | SOT23-5 |

| LNK625DG-TL | POWER | 22+ | 100000 | SOP-8 |

| OPA4322AIPWR | TI | 22+ | 100000 | TSSOP14 |

| TLV75528PDRVR | TI | 22+ | 99000 | WSON-6 |

| TPS7A2025PDQNR | TI | 22+ | 78500 | X2SON-4 |

| TLV62568DBVR | TI | 22+ | 72000 | SOT23-5 |

| STM32L051K8U6TR | ST | 22+ | 60000 | QFN32 |

| SKY66421-11 | SKYWORKS | 22+ | 56500 | QFN16 |

| TPS7A1111PDRVR | TI | 22+ | 54000 | WSON6 |

| TLV62569PDDCR | TI | 22+ | 52000 | SOT23-6 |

| TLV62569DBVR | TI | 22+ | 48000 | SOT23-5 |

| TPS23753APWR | TI | 22+ | 40000 | TSSOP14 |

| NB691GG-Z | MPS | 22+ | 30000 | QFN |

| SN74AHC1G02DBVR | TI | 22+ | 27939 | SOT-23 |

| TPS63000DRCR | TI | 22+ | 23238 | VSON10 |

| TLV75533PDRVR | TI | 22+ | 21500 | WSON6 |

| NB687BGQ-Z | MPS | 22+ | 20000 | QFN |

| A3916GESTR-T-1 | ALLEGRO | 22+ | 17150 | QFN-20 |

| TPS62135RGXR | TI | 22+ | 15000 | VQFN11 |

| TLE2022AMDR | TI | 0803+ | 12500 | SOP8 |

| TPS23756PWPR | TI | 22+ | 12000 | HTSSOP-20 |